chip communicatio sine filo

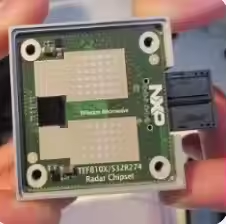

Unum chip communicationis sine filis fungitur ut fundamentum modernae connectionis, faciens transmissionem data inter apparatus sine connectionibus physicis. Haec circuitus integrati sophistici comprehendunt technologiam radio frequentiae progressivam, capacitatem tractandi signa, et systemas administrationis potentiae ad facilitandam communicationem sine filis fiduciam. Architectura chip solita includit processorem baseband, transceptor RF, amplificatorem potentiae, et varios modulos interface, operantes in harmonia ad transmittere et recipere signa wireless per multos protocollos tales qualis WiFi, Bluetooth, cellular, et normae IoT. Supportantes data rates a pluribus megabitibus ad gigabitum per secundum, hi chips integra plures normas wireless et frequentias, permitentes apparatus consistere connectionem constantem per varias rete. Features progressivi includunt protocollum securitatis inserti, administrationem potentiae adaptivam pro vita batteriae extenta, et algoritmos mitigationis interference intelligentis. Applicationes extendunt per electronicas consumer, systemas automotive, automation industrialem, apparatus medicalium, et technologiam domus smart, facientes hos chips componentes necessarios in mundo nostro crescenter connecto.